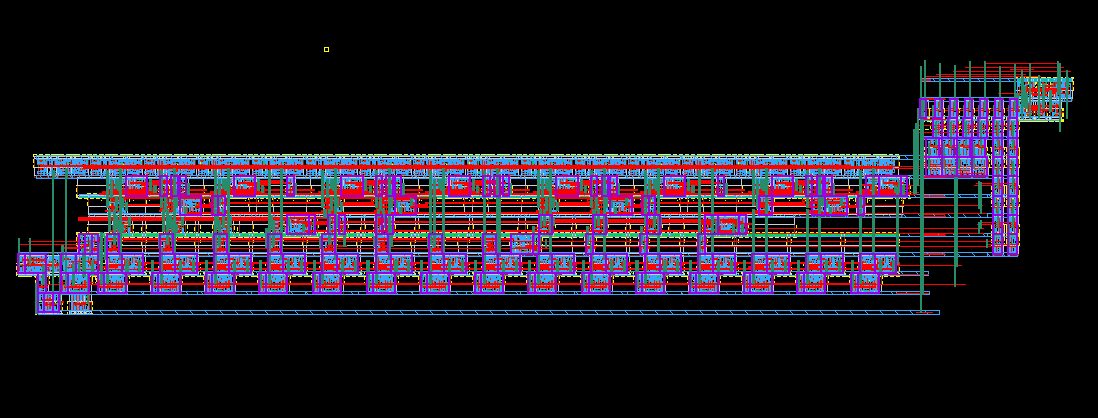

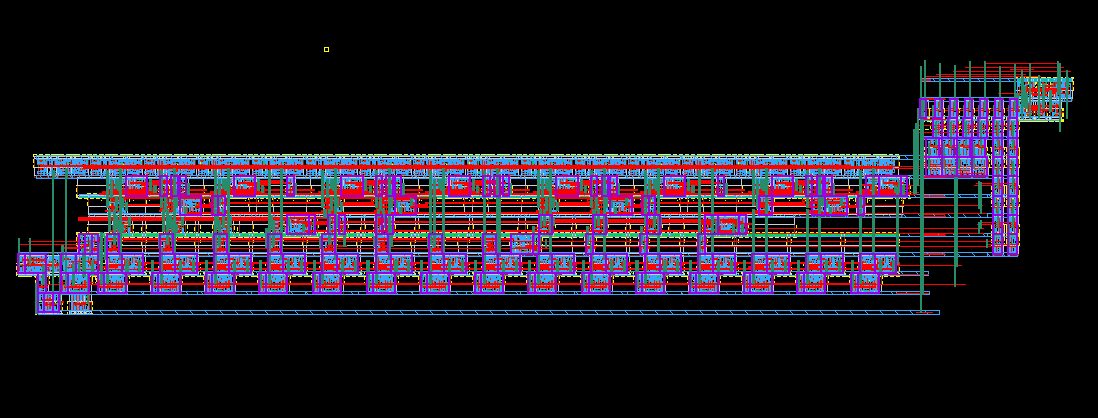

Layout Snapshot

A 16-bit Arithmetic Logic Unit (ALU) designed using the Sklansky Adder architecture, which a type of tree adder. The ALU supports Addition, Subtraction, the AND and XOR operations. It was designed and laid out in the TSMC 65nm node in Cadence Virtuoso. It has a critical path delay of 660ps and a total area of 1500 µm². This project was done back in 2017 as part of my EE 476: Digital VLSI I class in the University of Washington.